是什么原因造成晶振相噪恶化?都有哪些优化策略

来源:http://www.taiheth.com 作者:泰河盛电子 2021年01月13

是什么原因造成晶振相噪恶化?都有哪些优化策略.

对于Oscillator产品来说,相位噪声是一项非常重要的性能特征,它对晶振的输出频率稳定性影响非常大,一般情况下,相位噪声越小,则表示晶振性能越好,输出信号稳定性越高,所以低相噪是未来的产品发展方向;但是在优化相噪之前或者是做策略之前必须要先了解是什么原因造成了相噪的恶化,这样才能对症下药.

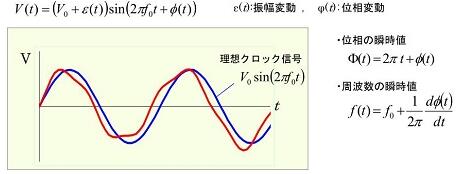

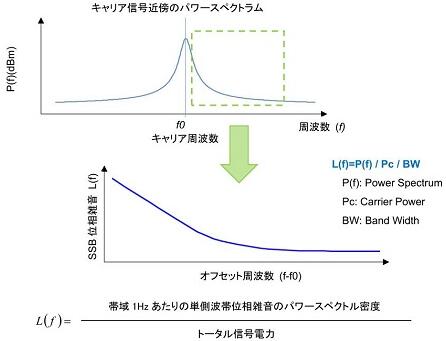

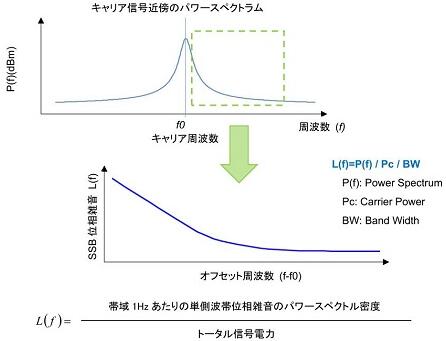

事实上,从某种意义上来看石英晶体振荡器的相噪和抖动是一样的,只是两者是对同种现象的两种不同的定量方式罢了.图1显示了具有理想正弦波相位项加相位变化Φ(t)形式的相位噪声的信号波形V(t).相位噪声和相位抖动是在频率区域和时间区域中获得的相位波动Φ(t). 相位噪声以相位波动Φ(t)的频率区域表示,并由Φ(t)的功率谱密度SΦ定义.实际上,通常使用在单边带中表示的SSB(单边带)相位噪声L(f),载波信号与总功率的比值以dBc/Hz计算,以相对于载波频率的偏移为水平轴.代表.

晶体振荡器的相位噪声在很大程度上取决于晶体振荡器的Q值和信号电平以及振荡电路的噪声性能.

晶体振荡器的相位噪声在很大程度上取决于晶体振荡器的Q值和信号电平以及振荡电路的噪声性能.

晶体振荡器的Q值对于改善相位噪声的载波频率附近的相位噪声尤其重要.无论偏移频率如何,信号电平越高,相位噪声电平越低.通过将信号电平设置为尽可能大的系统,可以降低相位噪声,但是可以应用于晶体振荡器的激励电平存在上限.如果激励水平过高,则可能会发生不必要的振动模式,并且振荡状态可能会变得异常.

泛音具有较高的Q值,并且在偏移附近很有效,但是要小心,因为在高激励电平下工作时,石英晶振和振荡电路的电阻损耗会变大,频率波动会变大,并且信号纯度会下降是必然的.

另外,随着功率的增加,由于晶体换能器的非线性引起的频率波动增加,因此在过度激励水平下的操作也会引起相位噪声的恶化.重要的是选择具有优异噪声性能的半导体器件.闪烁噪声会影响距载波附近大约10kHz中频附近的偏移频率,而热噪声会像信号电平一样均匀地影响整个偏移频带.

既然问题已经分析得差不多了,那么接下来就来看看应该怎么样优化有源晶振的这一性能了;首先要确保石英晶振振荡振动电路的Q值,晶体振荡器的Q值越高,振荡电路的电阻损耗越小,振荡环路的Q值越高;设备降噪是必须的,选择具有低噪声指数NF和闪烁转折频率的器件,以减少半导体噪声,例如热噪声,散粒噪声和闪烁噪声.

除此之外,PLL电路的倍频会导致相位噪声恶化.这点也要注意;同时还要尽可能增加振荡电路的激励水平.由于噪声特性是信号电平与噪声功率之间的相对值,所以信号电平越高,则越有利.然而,在平坦区域中使用晶体振荡器的激发能级特性是一个条件.泛音具有较高的Q值,在偏移附近非常有用.但是,当在高激励电平下工作时,晶体和振荡电路的电阻损耗会增加,并且由于频率波动,相位噪声会恶化,因此必须小心.

最后就是适当地在距电源和GND端子最短的地方放置一个旁路电容器,以抑制电源噪声.以上这些方法都能够很好的优化有源晶振相噪性能,对其性能的提升大有裨益.

由此看来,要优化有源晶振系列相位噪声,必须要注意的是晶体振荡器振荡电路的Q值,信号电平(也就是激励水平,值越大对降低相噪越有益);这两点可以说是主要决定性因素;当然,除开这两点之外,还要注意PLL电路的倍频;基本上能够影响相位噪声的就这三个方面的因素了,要优化的话也得从这三方面入手.

是什么原因造成晶振相噪恶化?都有哪些优化策略.

对于Oscillator产品来说,相位噪声是一项非常重要的性能特征,它对晶振的输出频率稳定性影响非常大,一般情况下,相位噪声越小,则表示晶振性能越好,输出信号稳定性越高,所以低相噪是未来的产品发展方向;但是在优化相噪之前或者是做策略之前必须要先了解是什么原因造成了相噪的恶化,这样才能对症下药.

事实上,从某种意义上来看石英晶体振荡器的相噪和抖动是一样的,只是两者是对同种现象的两种不同的定量方式罢了.图1显示了具有理想正弦波相位项加相位变化Φ(t)形式的相位噪声的信号波形V(t).相位噪声和相位抖动是在频率区域和时间区域中获得的相位波动Φ(t). 相位噪声以相位波动Φ(t)的频率区域表示,并由Φ(t)的功率谱密度SΦ定义.实际上,通常使用在单边带中表示的SSB(单边带)相位噪声L(f),载波信号与总功率的比值以dBc/Hz计算,以相对于载波频率的偏移为水平轴.代表.

晶体振荡器的Q值对于改善相位噪声的载波频率附近的相位噪声尤其重要.无论偏移频率如何,信号电平越高,相位噪声电平越低.通过将信号电平设置为尽可能大的系统,可以降低相位噪声,但是可以应用于晶体振荡器的激励电平存在上限.如果激励水平过高,则可能会发生不必要的振动模式,并且振荡状态可能会变得异常.

泛音具有较高的Q值,并且在偏移附近很有效,但是要小心,因为在高激励电平下工作时,石英晶振和振荡电路的电阻损耗会变大,频率波动会变大,并且信号纯度会下降是必然的.

另外,随着功率的增加,由于晶体换能器的非线性引起的频率波动增加,因此在过度激励水平下的操作也会引起相位噪声的恶化.重要的是选择具有优异噪声性能的半导体器件.闪烁噪声会影响距载波附近大约10kHz中频附近的偏移频率,而热噪声会像信号电平一样均匀地影响整个偏移频带.

既然问题已经分析得差不多了,那么接下来就来看看应该怎么样优化有源晶振的这一性能了;首先要确保石英晶振振荡振动电路的Q值,晶体振荡器的Q值越高,振荡电路的电阻损耗越小,振荡环路的Q值越高;设备降噪是必须的,选择具有低噪声指数NF和闪烁转折频率的器件,以减少半导体噪声,例如热噪声,散粒噪声和闪烁噪声.

除此之外,PLL电路的倍频会导致相位噪声恶化.这点也要注意;同时还要尽可能增加振荡电路的激励水平.由于噪声特性是信号电平与噪声功率之间的相对值,所以信号电平越高,则越有利.然而,在平坦区域中使用晶体振荡器的激发能级特性是一个条件.泛音具有较高的Q值,在偏移附近非常有用.但是,当在高激励电平下工作时,晶体和振荡电路的电阻损耗会增加,并且由于频率波动,相位噪声会恶化,因此必须小心.

最后就是适当地在距电源和GND端子最短的地方放置一个旁路电容器,以抑制电源噪声.以上这些方法都能够很好的优化有源晶振相噪性能,对其性能的提升大有裨益.

由此看来,要优化有源晶振系列相位噪声,必须要注意的是晶体振荡器振荡电路的Q值,信号电平(也就是激励水平,值越大对降低相噪越有益);这两点可以说是主要决定性因素;当然,除开这两点之外,还要注意PLL电路的倍频;基本上能够影响相位噪声的就这三个方面的因素了,要优化的话也得从这三方面入手.

是什么原因造成晶振相噪恶化?都有哪些优化策略.

正在载入评论数据...

相关资讯

- [2023-07-12]康纳温菲尔德推出符合Stratum3E...

- [2023-06-26]选择石英晶体要了解的必要参数,...

- [2023-06-25]艾伯康公司发布连续电压有源晶振...

- [2021-01-18]今日主题:什么样性能的石英晶振...

- [2021-01-13]是什么原因造成晶振相噪恶化?都...

- [2020-12-09]干货干货!爱普生旗下SG-8018系列...

- [2020-09-08]石英Crystal工作原理是怎样的,这...

- [2020-09-01]Oscillator的制造流程究竟是怎样...