你真正的了解什么是振荡器吗?

像石英晶体振荡器,陶瓷晶振,声表面滤波器这些产品一样,晶体振荡器也是有它自身所自带的一些参数,在上PCBA板,电路板,调试板上,都需要对应相关参数,才可以使用.尤其是一些比较高端产品应用,一定是要认准资料,并且一分一毫都不能有差的那种.差分晶体振荡器,时钟振荡器,实时时钟,恒温晶体这些产品相对来说产品要求相对的比较高一些,工程师在选型的时候就一定会特别注意所对应的参数要求,那么在工程师或者技术指导师的面前来说什么样的相关参数会如此重要呢??

标称频率:晶体振荡器的中心或标称输出频率。

封装:石英晶体振荡器采用各种类型的封装,从引脚孔到表面贴装类型。各种尺寸和功能适用于不同的应用。

频率容差:在室温下以百万分率(ppm)表示的与标称频率的偏差。(25°±5°C)

频率范围:可提供振荡器类型或型号的频段。

频率稳定性:与温度窗口25°C时的测量频率相比,即0°C至+ 70°C时的最大允许频率偏差。典型稳定性为±0.01%(±100 ppm)。

工作温度:输出频率和其他电气,环境特性符合规范的温度范围。

老化:一段时间内的相对频率变化。这种频率变化率通常是指数性的。通常,老化在1年内最大为±5 ppm。

存储温度:安装设备的温度范围(未施加电源电压),不会损坏或改变设备的性能。

频率与电源的变化:当电源电压在规定范围内变化时允许的最大频率变化(Vcc典型值±10%或±5%变化)。

电源电压(Vdd max):可以安全施加到Vcc端子的最大电压。TTL的最大电源电压为5.5V,HCMOS的最大电源电压为6V。

输入电压(VIN):可安全施加到振荡器输入端的最大电压。

输出高电压(VOH):在适当负载下振荡器输出端的最小电压。

输出低电压(VOL):正确加载时振荡器输出的最大电压。

电源电流(Icc):流入Vcc端子的电流相对于地。无负载测量典型电源电流。

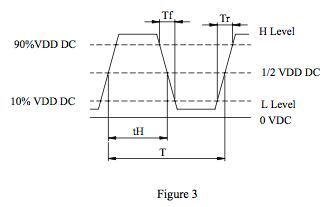

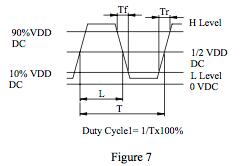

对称性或占空比:输出波形的对称性形成于指定的水平(TTL为1.4V,HCMOS为1 / 2Vcc,ECL为1/2波形峰值水平)。

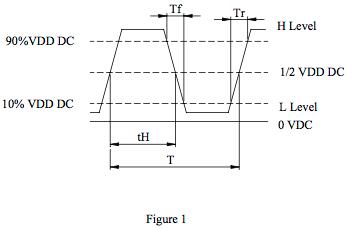

SYM = TH / T×100(%); 见图1。

上升时间(Tr):从低电平到高电平转换的波形上升时间,在指定电平下测量(HCMOS,ECL为20%至80%,TTL为0.4V至2.4V)。

下降时间(Tf):在指定级别测量的波形下降时间从高转变为低转换(HCMOS,ECL为80%至20%,TTL为2.4V至0.4V)。

扇出:振荡器驱动能力的度量,表示为可由单个输出驱动的输入数量。它可以用等效负载电容(CL)或由二极管,负载电阻和电容组成的TTL负载电路来表示。

抖动:振荡器输出的相位或频率调制。

HCMOS / TTL兼容:振荡器采用ACMOS逻辑设计,具有TTL和HCMOS负载的驱动能力,同时保持HCMOS的最小逻辑高电平。

三态使能:当输入保持OPEN或连接到逻辑“l”时,发生正常振荡。当输入接地(连接到逻辑“0”)时,输出处于HIGH IMPEDANCE状态。输入端有一个内部上拉电阻,允许输入保持开路。

输出逻辑:振荡器的输出设计用于满足各种指定逻辑,例如TTL,HCMOS,ECL,正弦波,限幅正弦波(DC截止)。

谐波失真:由与目标信号频率相关的不需要的谐波频谱分量引起的非线性失真。每个谐波分量是电功率与期望信号输出电功率之比,并且以dBc表示,即-20dBc。当需要干净且失真较小的信号时,谐波失真规范在正弦输出中尤为重要。

相位噪声:衡量振荡器的短期频率波动。它通常被指定为在距离载波的指定偏移频率处的1Hz带宽中的单边带(SSB)功率密度。它以dBc / Hz为单位。

待机:暂时关闭振荡器和其他分频器以节省功率的功能。逻辑“0”将启用待机模式。待机模式下的禁用电流从几微安到几十微安不等(典型值为5pA)。由于振荡停止,在输出稳定之前最多有10 ms(相同的启动时间)。

VCXO技术术语

控制电压(Vc):施加到VCXO输入的外部电压。通过改变电压,频率相应地变化。

典型的Vc为0 VDC至5 VDC,0.5 VDC至4.5 VDC,以及0.15 VDC至3.15 VDC。

偏差或频率可牵引性:输出频率相对于控制电压变化的最小变化。单位以ppm为单位。标准可牵引力最小为±50 ppm或最小为±100 ppm。

最大可牵引性:最大控制电压允许的最大频率变化(正向传递函数)。以ppm为单位测量。

传递函数:频率变化方向与控制电压变化的关系。如果在增加控制电压时频率上升,则称转移是正的。如果频率在增加Vc时下降,则传递函数为负。

输入阻抗: VCXO网络输入端口与电压控制源之间的隔离度量。典型输入阻抗> 10KHz时> 50kohms。

线性度:与频率与控制电压曲线的最佳直线斜率的偏差。典型线性度为±20%或±10%。

调制带宽:相对于1KHz输入调制频率的最小±3dB带宽频率。

中心频率或标称频率:用户指定的中心控制电压频率。中心频率的标准控制电压为VVD = 5 VDC时为2.5 VDC,Vcc = 3.3 VDC时为1.65 VDC。

振荡器应用说明

振荡器是产生连续输出信号的电路; 因此它被称为信号发生器。当产生的信号是恒定幅度和频率的正弦波时,振荡器电路称为正弦波发生器。振荡器可以在数字逻辑系列中产生方波信号,例如TTL,CMOS或ECL / PECL。

振荡器可以分为三个明确的部分:

(1)放大器

(2)反馈连接

(3)频率确定部件。

振荡的要求

如果电路由两个最低要求组成,则电路将振荡:

(1)正反馈

(2)环路增益大于1

当我们将放大器的输出连接到其输入时,提供反馈。如果反馈的输出与输入“异相”,则电路具有负反馈(NFB)。如果输出的反馈与输入同相,则电路具有正反馈(PFB)。

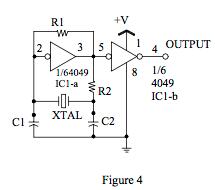

PIERCE振荡器电路

优点:

(1)在串联谐振处或附近运行(距离Fs约5ppm至200ppm)。(2)短期稳定性非常好。

(3)在1 kHz至200 MHz的任何频率下工作。

(4)电路提供大输出信号。

(5)以低功率驱动晶体。

(6)振荡频率对串联

电阻或并联电容的微小变化几乎不敏感。

电路配置:

•在大多数皮尔斯电路中,放大器仅由一个晶体管组成。输出可以缓冲以提供数字逻辑兼容输出(TTL或HC-CMOS

•Pierce放大器可以设计为CMOS,TTL和ECL中的数字逻辑元件;低频CMOS,中频TTL和ECL对于高频率。

晶体振荡器中的三态控制

大多数数字系统使用由两个状态级别0和1表示的二进制数系统。在某些特殊应用中,需要第三状态(Hi阻抗输出)。TTL,HCMOS或HCMOS晶体振荡器提供三态输出或三态启用/禁用功能。其常见应用包括自动测试,总线布线数据传输。

这三种状态是低,高和高阻抗(Hi Z或浮动)。高阻抗状态的输出表现得好像它与电路断开,除了可能有小的漏电流。三态器件具有使能/禁止输入,通常在几乎任何封装的引脚1上。当使能为高电平或悬空时,器件振荡(输出高电平和低电平),当引脚1接地(逻辑“0”)时,器件进入高阻态。

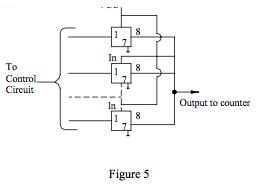

总线是一组通用的线路,通常用于数据传输。三态总线有几个三态输出连接在一起。通过控制电路,总线上的所有设备(除了一个)都具有高阻抗状态的输出。其余器件使能,驱动高低输出总线。

三态功能的其他应用是用于自动测试设备(ATE)。几个振荡器的输出连接在一起。对于控制电路,所有振荡器都有一个处于高阻态的输出。选择的唯一振荡器将从计数器读出其频率。(图5)

在三态函数生效之前总会有一些延迟。在两个转换(禁用和启用时)都会发生此效果。从低电平开始的三态输出禁止时间是tPLZ,三态到低电平的输出使能时间是tPZL。(图6)

CMOS

上升和下降时间CMOS技术的上升和下降时间取决于其速度(CMOS,HCMOS,ACMOS,BICMOS),电源电压,负载电容和负载配置。CMOS 40000系列的典型上升和下降时间为30ns,HCMOS为6ns,而ACMOS(HCMOS,TTL兼容)的最大上升和下降时间为3 ns。典型的上升和下降时间在其波形水平的10%至90%之间测量。(见图7)

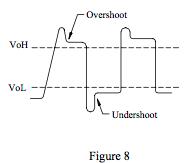

ACMOS输出终止技术

由于ACMOS(HCMOS / TTL兼容)器件的快速转换时间,在测试或测量电气性能特性时必须使用正确的端接技术。端接通常用于解决电压反射问题,这实质上导致时钟波形中的步骤以及过冲和下冲。这可能导致错误的数据时钟,以及更高的EMI和系统噪声。

由于PC板上的迹线长度及其负载配置,还需要端接。有三种终止时钟轨迹的通用方法,即将器件的输出阻抗与线路阻抗相匹配的过程:

方法1:串联终端(图9)在串联终端中,阻尼电阻靠近时钟信号源放置。Rs的值必须满足以下要求:Rs≥ZT - Ro

方法2:上拉/下拉电阻(图10)在上拉/下拉终端中,组合的戴维宁等效于迹线的特征阻抗。这可能是最干净的,并且不会产生反射,也会降低EMI。RT~ZT

相关资讯

- [2024-05-22]Statek低频振荡器CXOLP4SNSM4-8...

- [2024-03-08]32.768KHz振荡器比普通音叉晶振...

- [2023-10-19]美国ITTI晶振发表对石英晶体和振...

- [2023-10-19]ITTI晶振揭秘CRYSTAL DEVELOPME...

- [2023-10-17]ITTIA晶振是石英行业令人兴奋的...

- [2023-09-28]Crystek最新的CVCO33BE-2352-24...

- [2023-09-26]领先全球的Hosonic晶振品牌介绍...

- [2023-09-23]遥遥领先的思佳讯电子采用第四代...

.jpg)